182 183

182

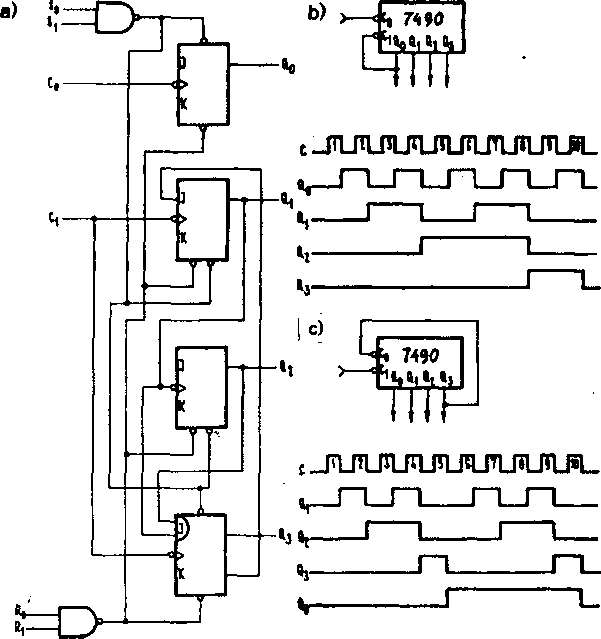

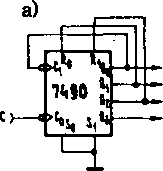

Rys. 5.66. Dekada 7490: a) schemat, b, c) sposoby łączenia

(rys. 5.66b). Dekada z dwójką liczącą na końcu (rys. 5-66c) liczy w kodzie dwupiątkowym (buąuinary codę), w którym najbardziej znaczący bit zmienia się co pięć stanów. Dekada taka, pracując jako dzielnik częstotliwości 1:10, daje na wyjściu przebieg prostokątny o wypełnieniu 0,5.

Stosując opisaną metodę zamiany licznika synchronicznego na asynchroniczny można łatwo sprawdzić, te asynchroniczny licznik binarny o pojemności 2® składa się z N połączonych szeregowo dwójek liczących, które można uzyskać z dowolnych przerzutnlków łącząc je jak na rys. 5-67.

o

Rys. 5.67. Łączenie przerzutników dla uzyskania dwójki liczącej

3.9.4. Skracanie cyklu w licznikach. MSI

Często, np. w dzielnikach częstotliwości,zachodzi potrzeba zbudowania licznika o pojemności niemożliwej do uzyskania przez łączenie szeregowe scalonych liczników dziesiętnych i binarnych, lub ich dostępnych fragmentów. Czytelnik nie pozostaje Już bezradny w tej sytuacji, dysponując umiejętnością zaprojektowania takiego licznika w wersji synchronicznej i ewentualnego przekształcenia go w prostszą wersję asynchroniczną. Przekształ- _ cenie takie Jest często możliwe ze względu na to, że kod licznika pracującego Jako dzielnik częstotliwości Jest dowolny i można go dobrać tylko pod kątem uproszczenia budowy licznika. Spośród innych możliwych metod na uwagę zasługuje metoda skracania cyklu w licznikach scalonych. Polega ona na wymuszeniu przeskoku pomijającego nadmiarową liczbę stanów. Omówimy to osobno dla liczników szeregowych i równoległych.

Skracanie cyklu w asynchronicznych licznikach MSI

Scalone liczniki asynchroniczne wyposażone są w wejścia zerujące, toteż skracanie cyklu odbywa się poprzez zerowanie licznika po przejściu zadanej liczby stanów.

Przykład 3.10

Dysponując dekadą 7490 zbudować licznik modulo 6.

Przyjmijmy, że dekada połączona Jest Jak na rys. 5.66b i pracuje w kodzie BCD. W celu skrócenia cyklu do 6 stanów należy Ją wyzerować po zliczeniu 6 impulsów, tzn. z chwilą osiągnięcia stanu (0110)2 = (6)1Q. W tym celu wystarczy połączyć z RQ oraz Q2 z R^, Jak na rys. 5.68a.

b)

* m_m m m m_rq_m

«. czn_i—i i—i

-O-

-U

a

STAN

cKwaowy

Rys, 5*68» Licznik mod 6 zbudowany z dekady 7*90: a) schemat, b) wykresy

czasowe

Wyszukiwarka

Podobne podstrony:

dwojkaliczaca jPodatkowe Nr 38 Dwójka licząca na przerzutnikach Rys. 3.1 Przykłady konwersji przerzn

schemat sposoby laczenia materialow SPOSOBY ŁĄCZENIA MATERIAŁÓWłączenie materiałów nierozłączne rozł

182 183 182 I a)i=t> b) -«oc jnjnjminjnjTUiułLPL c) 7490RTFc j^unjnjnju*unj^uiLPL Rys. 5.66. Deka

66 (63) □ SCHEMAT NR 06 - NASTA WA PRĘDKOŚCI OBROTOWEJ (Sprawny regulator prędkości obrotowej) (rys.

Str 182 Rys. 13.4 prawdopodobieństwo, p [%] Rys. 13.5 182

29 (314) 182 1 f Rys. 18.1. Ruch kulki w ośrodku lepkim i działające na nią siły oraz rozkład prędk

89 (140) 182 Rys. 9.17. Jak rycie dachówką karpiówką w łuskę; rozstaw łat 16 en ny tylko jeden rząd

1tom190 7. ELEKTRONIKA 382 Rys. 7.66. Układy CMOS: a) schemat ideowy inwertora; b) schemat ideowy&nb

Image250 Schemat logiczny synchronicznego dwukierunkowego licznika dwójkowego (193) przedstawiono na

Image312 Schemat logiczny jednotetradowego sumatora w kodzie „+3” przedstawiono na rys. 4.357. Na ry

Image371 Schemat logiczny układu realizującego powyższe funkcje przełączające przedstawiono na rys.

img182 182 zaś "1" przemiennie w impulsy dodatnie i ujemne, rysunek 1.67f. Graf kodu AMI j

Schemat zastępczy diody rzeczywistej dla stanów dynamicznych przedstawiono na rys.2. Obok elementów

więcej podobnych podstron