Image143

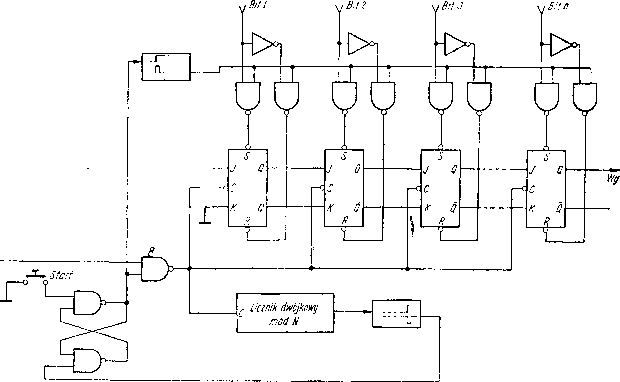

rys. 4.91. Impuls „start” powoduje wpisanie informacji do rejestru i odblokowanie bramki B. Informacja zapamiętana w rejestrze jest wyprowadzana bit po bicie (Wy) w takt impulsów przebiegu C. Po N impulsach przebiegu C informacja jest wyprowadzona z rejestru w postaci szeregowej, a bramka B ponownie zablokowana.

Rys. 4.91. Układ do równoległego wprowadzania i szeregowego wyprowadzania informacji

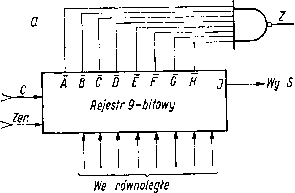

Na rysunku 4.92a przedstawiono schemat ideowy innego, prostszego układu zamiany informacji wprowadzonej równolegle na informację wyprowadzaną

|

A |

8 |

C |

D |

[ |

F |

G |

H |

J | |

|

Zen |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

m rótvn |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

i |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

2 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

3 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

4 |

0 |

0 |

0 |

0 |

/ |

0 |

0 |

0 |

0 |

|

5 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

6 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

8 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Rys. 4.92. Układ do równoległego wprowadzania i szeregowego wyprowadzania informacji

szeregowo. Zastosowany rejestr szeregowy powinien zawierać o jeden przerzut-nik więcej, niż liczba bitów informacji wejściowej. Działanie układu wyjaśnia tabelka na rys. 4.92b. Po wyzerowaniu rejestru, przyjmuje on następujące

153

Wyszukiwarka

Podobne podstrony:

Image451 Działanie układu jest następujące. Sygnał „Start” powoduje wpisanie do licznika nastawy N o

Zastaw ustanowiony wg przepisów KC. Można ustanowić na statku wpisanym i niewpisanym do rejestru okr

Image121 00 ... O i 11 ... 1 (rys. 4.66). Wybór sposobu wprowadzania informacji do rejestru lub jej

Image122 a Rys. 4.62 Układ służący do równoległego wprowadzania informacji z czterech źródeł do reje

Image124 Rys. 4.66. Układ służący do równoległego wyprowadzania informacji z rejestru Q

Image134 Adres słowa Rys. 4.80. Układ wprowadzania informacji ze wspólnej szyny do rejestrów równole

Image138 gu C, ustawienie stanu 1 na wyjściu Qx przerzutnika Plt jednocześnie zaś do rejestru Rx zos

Image144 stany: A = 1, B — C — ... / = 0. Następnie informacja jest wpisywana do rejestru. Po ośmiu

Image121 00 ... O i 11 ... 1 (rys. 4.66). Wybór sposobu wprowadzania informacji do rejestru lub jej

Image144 stany: A = 1, B — C — ... / = 0. Następnie informacja jest wpisywana do rejestru. Po ośmiu

Image112 Rys. 4.49. Ilustracja definicji czasów propagacji sygnałów od wejść synchronizujących do wy

Image134 Rys. Zmienne stanu — droga X0— prędkość X7— przyspieszenie w wyróżnionych chwilach czasu: 1

Image137 Rys. 4.83 Zespół rejestrów buforowych o pojemności 8 słów 8-bitowych 2 rozdzielacza Rys. 4.

więcej podobnych podstron