Image585

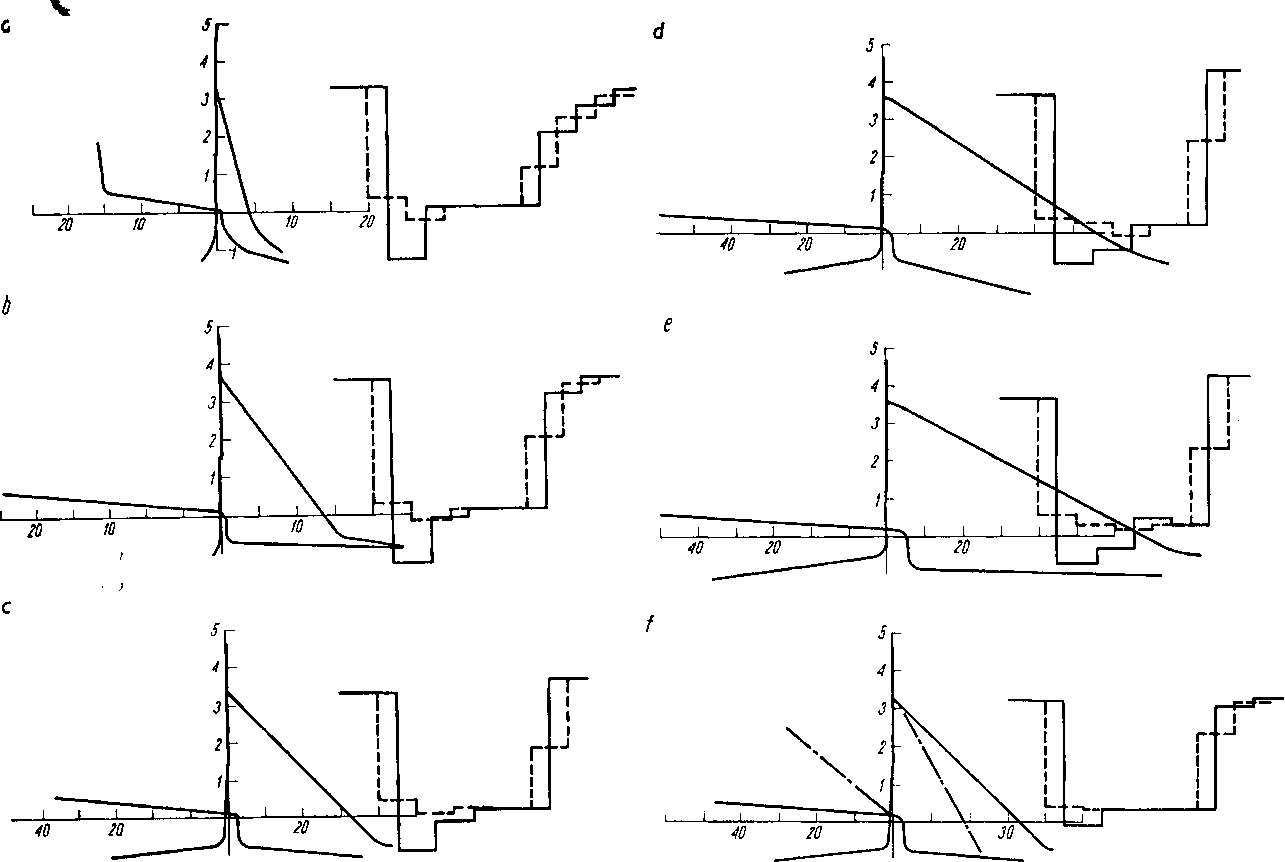

Rys. 4.781. Diagramy Bergerona dla bramek TTL

*> z serii L (dla Z# «* 100 fi), b) z serii LS (dla Z, =* 150 fi), c) z serii standardowej (dla Z, - 100 fi),

d) z serii H (dla Z* ™ 100 fi), e) z serii S (dla Z# * 75 fi), f) z serii standardowej z rezystorem szeregowym 75 fi (dla Z# = 100 fi)

/li

i

Wyszukiwarka

Podobne podstrony:

Image586 Na rysunku 4.781 przedstawiono diagramy Bergerona dla różnych typów bramek TTL. Dołączenie

Image153 1000 rotoo Funkcja opisująca sprzężenie: F‘C®D Rys. 4.106. Diagram stanów dla rejestru lini

Image572 4.8.8. Układy wyjściowe mocyWzmacniacze mocy sterowane z bramek TTL Moc sygnału wyjściowego

■ , ■ Monety Rys. 4 Niepełny diagram poziomu 0 dla automatu 5. Do opisu procesu

Image101 — układ przesuwania poziomu napięcia, — typowy dla bram

Image573 Rys. 4.757. Schematy ideowe układów wysterowania tranzystorów krzemowych n-p-n ze standardo

Image096 Konfiguracje stopni wyjściowych bramek TTL Tablica 4.3 Stopnie wyjściowe Zalety Wady a) Ukł

Image154 Na rysunku 4.108 przedstawiono diagram stanów dla rejestru liniowego o n = 5 i sprzężeniu F

Image503 Rys. 4.635. Schemat logiczny programowanego generatora par impulsówa --(25-55)Tb i Rys. 4.6

Image506 Rys. 4.641. Schemat logiczny programowanego generatora impulsów o dowolnych wzorach zero-je

Częsc 1 11 rys. 1.9. położenie środka ścinania Dla ceownika: Środek ścinania znajduje się w

więcej podobnych podstron