Slajd19 (159)

BQ48o2 - PARAJLLEL REAL-TIME CLOCK

AcJdress

J«- lAW --►r— lWR2

tAS - tcw -H

NOTES: A.

B.

C.

D.

E.

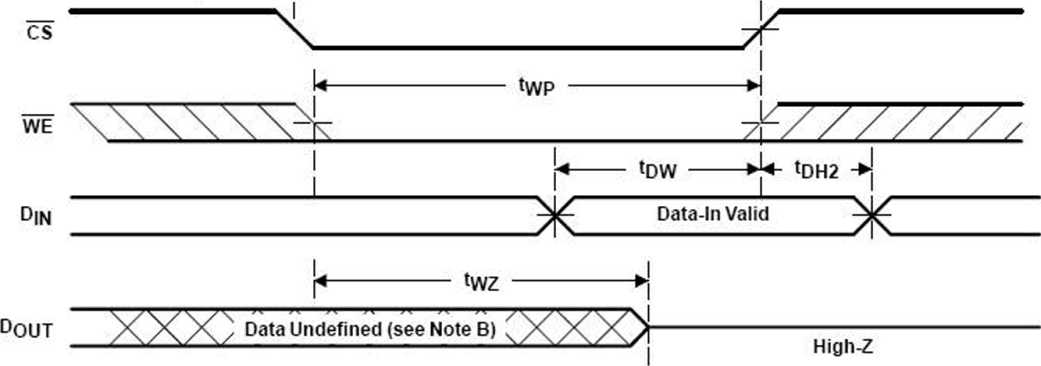

WE or CS must be held high during address transition.

Because l/O may be active (OE Iow) during the period, data input signals of opposite polarity to the outputs must be applied. If OE is high, the 1/0 pins remain in a State of high impedance.

EithertwRi or tyyR2 must 1)e met.

EithertDHl °rtDH2mustbe met.

Figurę 8. Write Cycle No. 2 - CS Controlled

Wyszukiwarka

Podobne podstrony:

Slajd18 (161) BQ48o2 - PARAJLLEL REAL-TIME CLOCK NOTES A WE isheld high for a read cycle. _ B Deyice

20610 Slajd21 (159) BQ48o2 - PARAJLLEL REAL-TIME CLOCK Table 2. Clock and Control Register

Slajd20 (163) BQ48o2 - PARAJLLEL REAL-TIME CLOCK NOTES: A. PWRIE set to 1 to enabl

Slajd22 (156) BQ48o2 - PARAJLLEL REAL-TIME CLOCK Table 3. Clock and Contro! Register

Slajd24 (150) BQ48o2 - PARAJLLEL REAL-TIME CLOCK Table 5. Periodic Interrupt Rates REGISTER

Slajd25 (146) BQ48o2 - PARAJLLEL REAL-TIME CLOCK Table 6. Alarm Frequency 1h 3h 5h 7h ALARM

22919 Slajd16 (165) BQ48o2 - PARAJLLEL REAL-TIME

więcej podobnych podstron