31483 p1030020

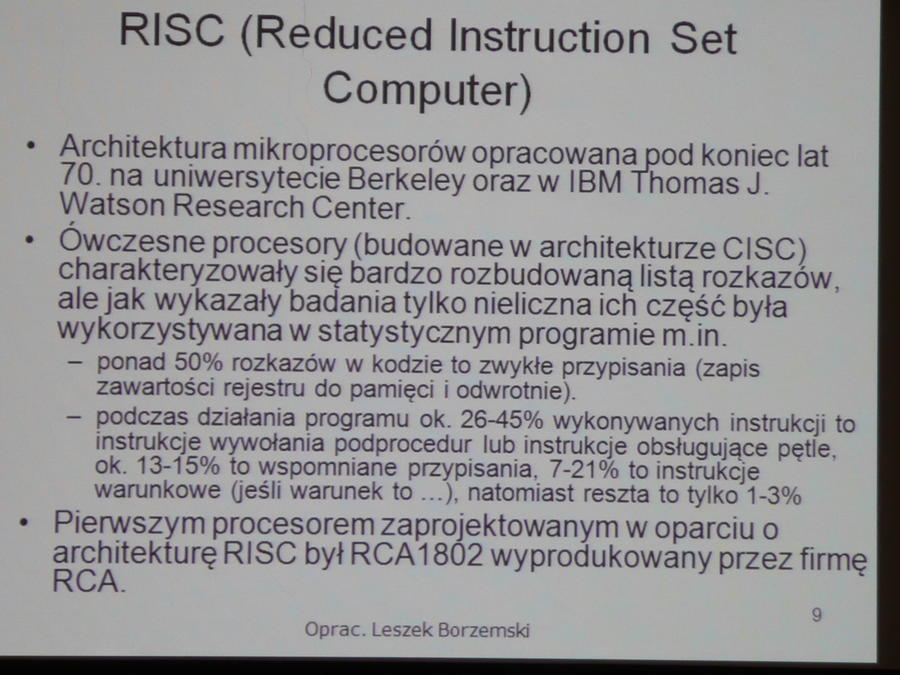

RISC (Reduced Instruction Set Computer)

• Architektura mikroprocesorów opracowanapod koniec lat 70. na uniwersytecie Berkeley oraz w IBM Thomas J. Watson Research Center.

• Ówczesne procesory (budowane w architekturze CISC) charakteryzowały sie bardzo rozbudowaną listą rozkazów, ale jak wykazały badania tylko nieliczna icn część była wykorzystywana w statystycznym programie m.in.

- ponad 50% rozkazów w kodzie to zwykłe przypisania (zapis zawartości rejestru do pamięci i odwrotnie).

- podczas działania programu ok. 26-45% wykonywanych instrukcji to instrukqe wywołania podprocedur lub instrukcje obsługujące pętle, ok. 13-15% to wspomniane przypisania, 7-21% to instrukcje warunkowe (jeśli warunek to ...), natomiast reszta to tylko 1-3%

• Pierwszym procesorem zaprojektowanym w oparciu o architekturę RISC był RCA1802 wyprodukowany przez firmę

Oprać. Leszek Borzemskf

9

Wyszukiwarka

Podobne podstrony:

Architektura procesora RISC Cechy architektury RISC (Reduced Instruction Set Computer): *

Architektura procesora RISC Cechy architektury RISC (Reduced Instruction Set Computer): ■k Zredukowa

p1030019 CISC (Complex Instruction Set Computer) • Projektanci pierwszych procesor

49839 Slajd23 (108) Przetwarzanie rozkazówRISC - reduce instruction set Computer CISC - complex inst

Architektura procesora CISC Cechy architektury CISC (Complex Instruction Set Computers): *

p1030018 Procesory... Ogólnego przeznaczenia - CISC (Complex Instruction Set Compu

Architektura procesora CISC Cechy architektury CISC (Complex Instruction Set Computers): *

P1020411 Student’s name * Computer architecture - the finał examination - duration of the examinatio

p1030021 RISC • Zredukowana lista rozkazów (nie przekracza kilkudziesięciu) •

p1030021 RISC • Zredukowana lista rozkazów (nie przekracza kilkudziesięciu) •

25 (97) d)wykonanie instrukcji SET TRANSACTION RE AD ONLY. ló.Użycie których metod może spowodować z

więcej podobnych podstron