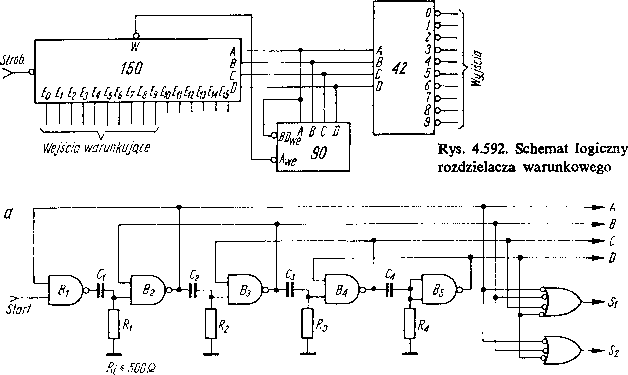

Image475

8( - Bramki z układem Schmitta

b

Start U ”

St

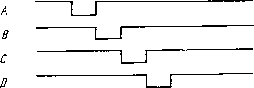

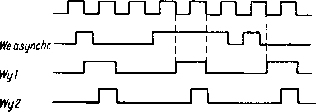

Rys. 4.593. Autorozdzielacz 4-wyjściowy

a) schemat logiczny, b) przebiegi ilustrujące działanie układu

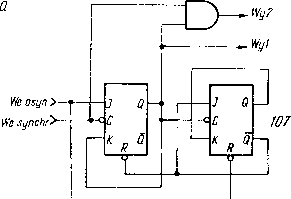

4.7.3.6. Układy synchronizacji przebiegów asynchronicznych

W wielu przypadkach występuje potrzeba synchronizacji informacji, pojawiającej się w sposób asynchroniczny w stosunku do przebiegu synchronizującego.

Przykład rozwiązania układu synchronizacji przebiegów asynchronicznych przedstawiono na rys. 4.594. W układzie tym uzyskuje się impulsy o stałej

We synchr

Rys. 4.594. Układ synchronizacji przebiegów asynchronicznych

a) schemat ideowy układu, b) przebiegi napięć ilustrujące działanie układu

Wyszukiwarka

Podobne podstrony:

026 3 26 Sterowanie logiczne i sekwencyjne start slup Rys. 3.2. Schemat logiczny układu włączania z

slide0376 image406 0CATIA V5 - [Productl] Start TeamPDM File Edit View Insert lools Ąnalyze Window H

slide0380 image423 0CATIA V5 - [Productl] Start TeamPDM File Edit View Insert Sprzęgło czOl (czOl.l)

slide0384 image440 0CATIA V5 - [Productl] Start TeamPDM File Edit View Insert lools Ąnalyze Window H

slide0391 image470 0CATIA V5 - [Productl] Start TeamPDM File Edit View Insert lools Ąnalyze Window

CMOS3 4093 Cztery 2-wejściowe bramki NAND Schmitta • Cz83 propagacji: 300ri8 przy

Image477 start Start J Uniwibrator Słowo kodowo k Czas To kreślony jest przez słowo kodowe k Rys. 4.

Na rys. 2. przedstawiono przykład realizacji bramki typu inwerter w technologii CMOS wraz z układem

Image477 start Start J Uniwibrator Słowo kodowo k Czas To kreślony jest przez słowo kodowe k Rys. 4.

Image098 r Bramka LUB-NIE (NOR) oraz LUB (OR) Schemat elektryczny bramki LUB-NIE — 02 przedstawiono

Image099 W przypadku dołączenia do tej bramki ekspanderów (rys. 4.20) układ realizuje funkcję: F = A

Image114 Przerzutnik JK-MS — 72 przedstawiono na rys. 4.53. Bramki 1 i 2 realizują funkcje K = KX*K2

Image143 rys. 4.91. Impuls „start” powoduje wpisanie informacji do rejestru i odblokowanie bramki B.

Image236 Rys. 4.245. Dekada licząca w kodzie 8421 z układem synchronicznego wpisywania

Image325 Układ przedstawiony na rys. 4.372, spełniający równanie (14), jest układem najszybszym, gdy

więcej podobnych podstron