Image100

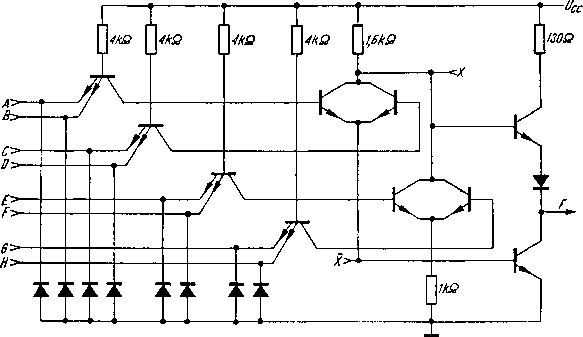

Na rysunku 4.22 przedstawiono schemat ideowy bramki I-LUB-NIE realizującej funkcję:

F= AB+CD + EF+GH

Bramka ta umożliwia dołączenie czterech ekspanderów.

Rys. 4.22. Bramka I-LUB-NIE (AND-OR-NOT) z czterema bramkami iloczynowymi

Bramka I-NIE (NAND) z układem Schmitta

Schemat elektryczny bramki I-NIE (NAND) z układem Schmitta przedstawiO' no na rys. 4.23. W jednej obudowie znajdują się cztery identyczne bramki.

W skład bramki wchodzą następujące układy:

— układ wejściowy,

— przerzutnik Schmitta,

110

Wyszukiwarka

Podobne podstrony:

Image141 Na rysunku 4.88 przedstawiono schemat ideowy pamięci szeregowej, zbudowanej z rejestrów prz

Image145 Na rysunku 4.95 przedstawiono schemat ideowy wykorzystania rejestru 198 jako licznika pierś

Image146 Wyjścia Na rysunku 4.98 przedstawiono schemat ideowy układu licznika Johnsona mod. 16 zbudo

Image125 Na rysunku 4.68 przedstawiono schemat logiczny czterobitowego rejestru przesuwającego, zbud

Image257 Na rysunku 4.280 przedstawiono schemat ideowy układu, umożliwiającego realizację operacji X

Image274 Na rysunku 4.305 przedstawiono schemat ideowy kaskadowego połączenia trzech programowanych

Image517 Na rysunku 4.658 przedstawiono schemat ideowy translatora sygnałów, w którym czasy narastan

Image097 Na rysunku 4.15b przedstawiono charakterystykę przełączania bramki oraz odpowiadającą jej z

Image098 r Bramka LUB-NIE (NOR) oraz LUB (OR) Schemat elektryczny bramki LUB-NIE — 02 przedstawiono

Image136 Na rysunku 4.82 przedstawiono przykład rozwiązania pamięci typu RAM, zbudowanej z rejestrów

Image150 Na rysunku 4.102 przedstawiono dwa przykłady rejestrów liniowych zawierających cztery przer

Image154 Na rysunku 4.108 przedstawiono diagram stanów dla rejestru liniowego o n = 5 i sprzężeniu F

więcej podobnych podstron